compteur sychrones 2018 3ST.pdf

Nom original: compteur sychrones-2018-3ST.pdf

Titre: LES SYSTEMES SEQUENTIELS 2007

Auteur: ATEF

Ce document au format PDF 1.6 a été généré par Acrobat PDFMaker 19 pour Word / Adobe PDF Library 19.21.90, et a été envoyé sur document-pdf.fr le 08/02/2020 à 01:53, depuis l'adresse IP 197.31.x.x.

La présente page de téléchargement du fichier a été vue 1801 fois.

Taille du document: 494 Ko (5 pages).

Confidentialité: fichier public

Aperçu du document

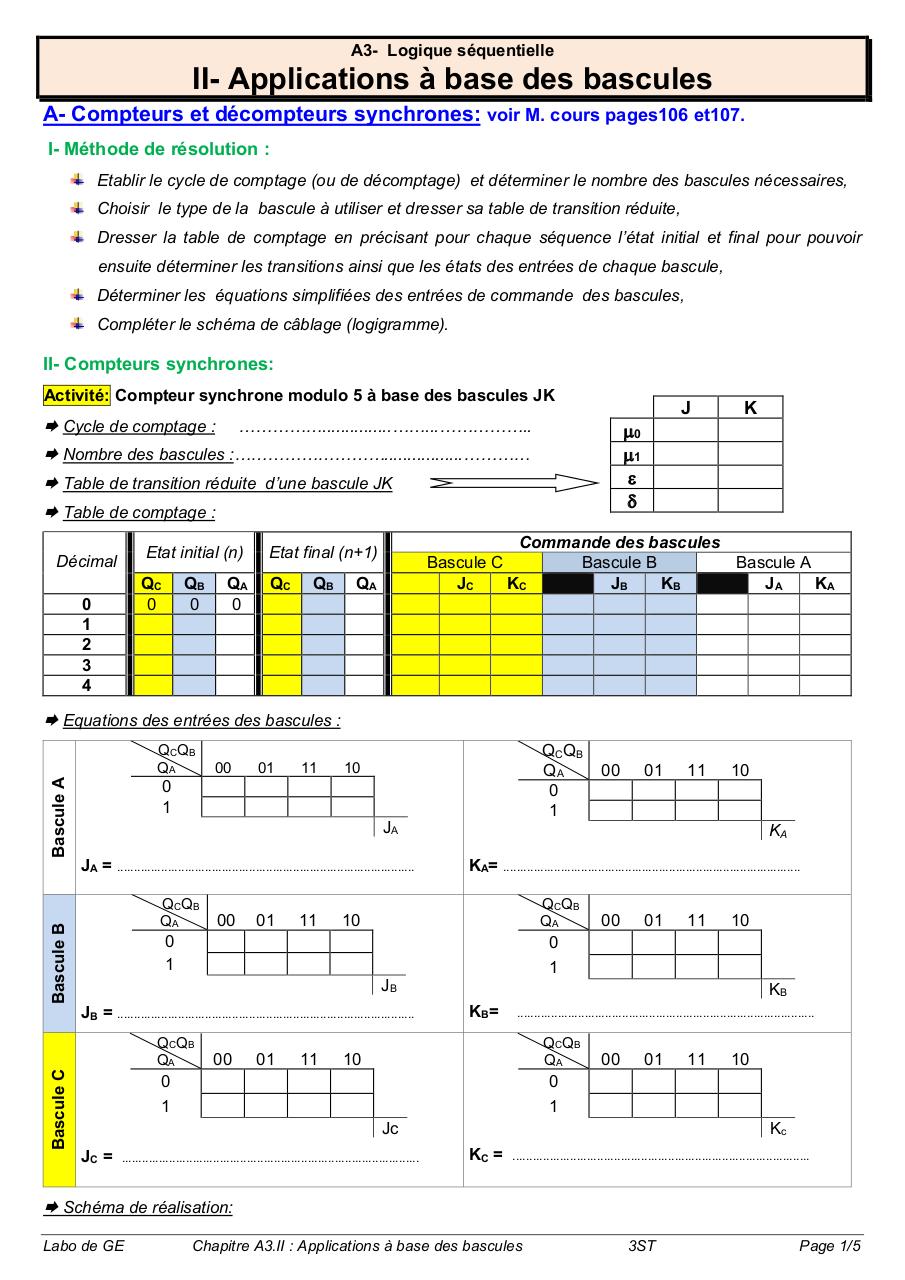

A3- Logique séquentielle

II- Applications à base des bascules

A- Compteurs et décompteurs synchrones: voir M. cours pages106 et107.

I- Méthode de résolution :

Etablir le cycle de comptage (ou de décomptage) et déterminer le nombre des bascules nécessaires,

Choisir le type de la bascule à utiliser et dresser sa table de transition réduite,

Dresser la table de comptage en précisant pour chaque séquence l’état initial et final pour pouvoir

ensuite déterminer les transitions ainsi que les états des entrées de chaque bascule,

Déterminer les équations simplifiées des entrées de commande des bascules,

Compléter le schéma de câblage (logigramme).

II- Compteurs synchrones:

Activité: Compteur synchrone modulo 5 à base des bascules JK

Cycle de comptage :

……………...............……...……………..

Nombre des bascules :……………………….................…………

Table de transition réduite d’une bascule JK

Table de comptage :

Décimal

0

1

2

3

4

Etat initial (n)

Etat final (n+1)

QC

0

QC

QB

0

QA

0

QB

J

µ0

µ1

ε

δ

K

Commande des bascules

Bascule C

Bascule B

Bascule A

JC

KC

JB

KB

JA

KA

QA

Bascule C

Bascule B

Bascule A

Equations des entrées des bascules :

Q CQ B

QA

0

1

00

01

11

JA

JA = ........................................................................................

Q CQ B

QA

0

1

00

01

11

Q CQ B

QA

JC =

0

1

JB

Q CQ B

QA

00

01

11

KB=

01

11

10

KA

Q CQ B

QA

0

1

Jc

KC =

00

01

11

10

KB

........................................................................................

10

........................................................................................

00

KA= ........................................................................................

10

JB = ........................................................................................

0

1

Q CQ B

QA

0

1

10

00

01

11

10

Kc

........................................................................................

Schéma de réalisation:

Labo de GE

Chapitre A3.II : Applications à base des bascules

3ST

Page 1/5

Activité: Réaliser l'activité 8 pages 74 et 75 du manuel des activités

IV- Décompteurs synchrones:

Activité: Décompteur synchrone modulo 4 à base des bascules D

Cycle de comptage :

Table de transition réduite d’une bascule D :

………………………………….

µ0

µ1

ε

δ

Nombre des bascules :

………………………………….

Etat

Etat final

initial (n)

(n+1)

QB

QA

QB

QA

Commande des

bascules

Bascule B Bascule A

DB

DA

QA

QB

0

1

0

1

DB

DB = ...........................

Bascule A

3

2

1

0

Equations des entrées des bascules :

Bascule B

Table de comptage :

Décimal

D

QA

QB

0

1

DA =

0

1

DA

...........................

Schéma de câblage

Activité: Réaliser l'activité 9 pages 76-77 du manuel des activités

B- Registre à décalage:

Lecture:

Consulter le manuel de cours pages 112 et 113.

Activité: Réaliser l'activité 10 pages 77 et 78 du manuel des activités

Labo de GE

Chapitre A3.II : Applications à base des bascules

3ST

Page 2/5

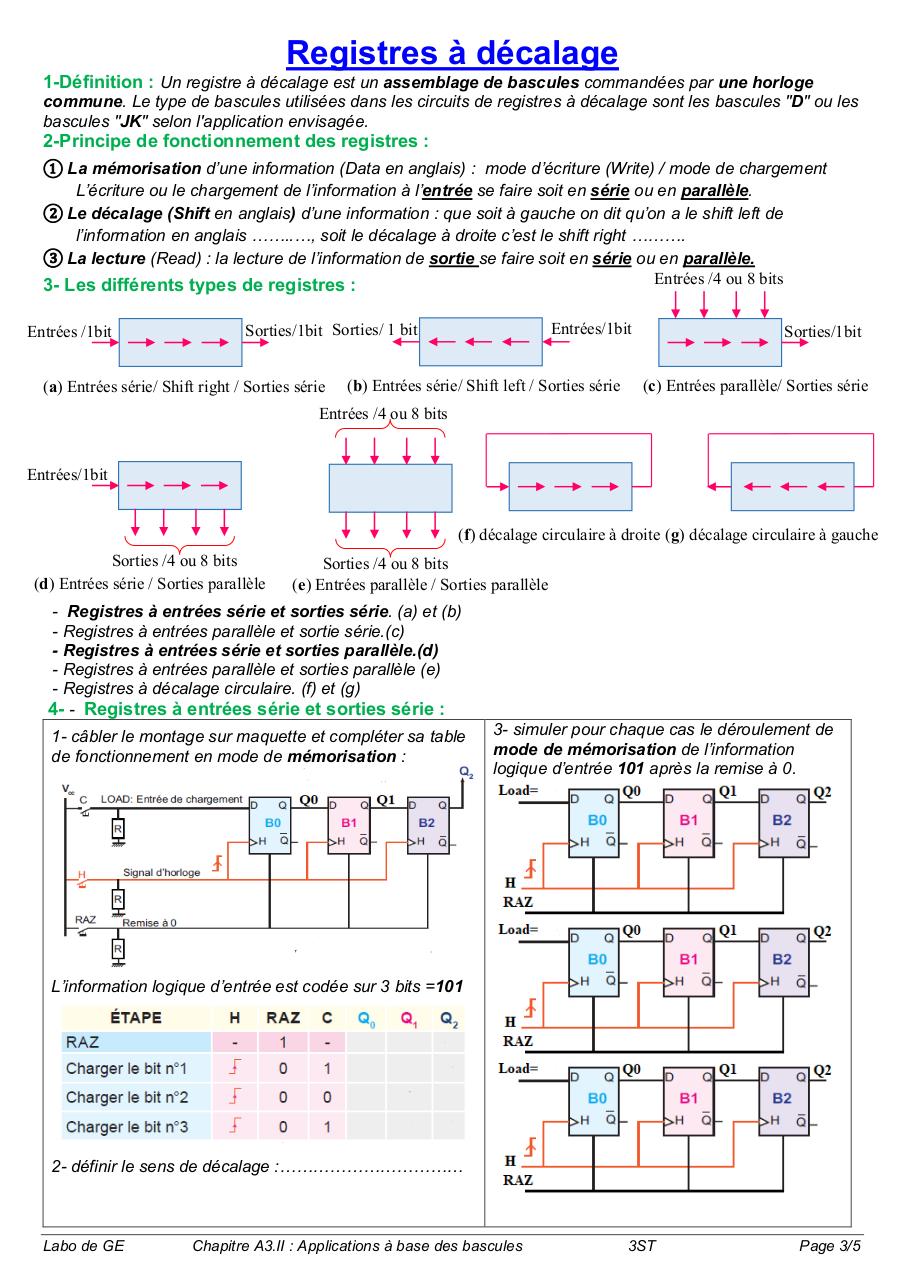

Registres à décalage

1-Définition : Un registre à décalage est un assemblage de bascules commandées par une horloge

commune. Le type de bascules utilisées dans les circuits de registres à décalage sont les bascules "D" ou les

bascules "JK" selon l'application envisagée.

2-Principe de fonctionnement des registres :

① La mémorisation d’une information (Data en anglais) : mode d’écriture (Write) / mode de chargement

L’écriture ou le chargement de l’information à l’entrée se faire soit en série ou en parallèle.

② Le décalage (Shift en anglais) d’une information : que soit à gauche on dit qu’on a le shift left de

l’information en anglais ……..…, soit le décalage à droite c’est le shift right ……….

③ La lecture (Read) : la lecture de l’information de sortie se faire soit en série ou en parallèle.

Entrées /4 ou 8 bits

3- Les différents types de registres :

Entrées /1bit

Entrées/1bit

Sorties/1bit Sorties/ 1 bit

(a) Entrées série/ Shift right / Sorties série

(b) Entrées série/ Shift left / Sorties série

Sorties/1bit

(c) Entrées parallèle/ Sorties série

Entrées /4 ou 8 bits

Entrées/1bit

(f) décalage circulaire à droite (g) décalage circulaire à gauche

Sorties /4 ou 8 bits

(d) Entrées série / Sorties parallèle

Sorties /4 ou 8 bits

(e) Entrées parallèle / Sorties parallèle

- Registres à entrées série et sorties série. (a) et (b)

- Registres à entrées parallèle et sortie série.(c)

- Registres à entrées série et sorties parallèle.(d)

- Registres à entrées parallèle et sorties parallèle (e)

- Registres à décalage circulaire. (f) et (g)

4- - Registres à entrées série et sorties série :

1- câbler le montage sur maquette et compléter sa table

de fonctionnement en mode de mémorisation :

3- simuler pour chaque cas le déroulement de

mode de mémorisation de l’information

logique d’entrée 101 après la remise à 0.

L’information logique d’entrée est codée sur 3 bits =101

2- définir le sens de décalage :……………………………

Labo de GE

Chapitre A3.II : Applications à base des bascules

3ST

Page 3/5

② 4 éme front :

4- sur maquette, compléter la table de fonctionnement en

mode de lecture de l’information de sortie 101 :

5- simuler pour chaque cas le déroulement de mode de

lecture de l’information logique de sortie 101.

① Etape initiale :

③ 5 éme front :

6-définir le type de registre :………………

……………………………………………….

…

5- - Registres à entrées série et sorties parallèle :

5-1 -Registres à entrées série et sorties parallèle avec bascule D à 4 bits :

1- Câbler le montage sur maquette et compléter sa table de

fonctionnement en mode de mémorisation :

RAZ Load CLK

Q0 Q1 Q2 Q3

0

1ére front

1

1

2éme front

0

1

3éme front

1

1

4éme front

0

1

2- déduire le mode de lecture de

l’information logique de sortie 1010.

………………………………aprés………

3-définir le type de registre :………………

……………………………………………….

5-2- Registres série / parallèle en circuit intégré 74HC164 :

5-2-1- Présentation :

Le circuit74HC164 est un registre à décalage série parallèle à 8 bits .il est composé :

-d’une entrée de remise à zéro asynchrone (MR).

-d’une entrée d’horloge clock puls (Cp).

- deux entrées de donnée(chargement) série : DSA et DSB.

- huit sorties de données parallèles (Q0 à Q7).

1-Symbole logique : 2- Symbole logique :

3- Brochages :

4- Structure interne :

Labo de GE

Chapitre A3.II : Applications à base des bascules

3ST

Page 4/5

5-2-2- Simulation de 74HCT164 :

Raz

0

1

1

1

1

1

1

1

1

1- Simuler le montage sous Proteus- Isis et compléter

sa table de fonctionnement en mode de

mémorisation :

L

1

0

0

1

1

0

0

1

Clk

1

1

1

1

1

1

1

1

Q0

Q1

Q2

Q3

Q4

Q5

Q6

Q7

2- comment faire la lecture de donnée de sortie :

La lecture finale est après …….. Front de clk sur

toutes les sorties en respectant que :

Le premier bit d'entré sera lu sur la sortie …

et le dernier bit d'entré sera lu sur la sortie….

5-2-3- Application de 74HCT164 :

Le chenillard peut désigner : un mouvement lumineux qui se produit en allumant et éteignant

successivement une série de lampes ou LED. L'effet se traduit par un déplacement de cette lumière

dans un sens choisi, par exemple de gauche à droite.

Labo de GE

Chapitre A3.II : Applications à base des bascules

3ST

Page 5/5

Télécharger le fichier (PDF)

compteur sychrones-2018-3ST.pdf (PDF, 494 Ko)